## CALCOLATORI ELETTRONICI B – 7 luglio 2008

| TR: |

|-----|

| ١   |

Scrivere chiaramente in caratteri maiuscoli a stampa

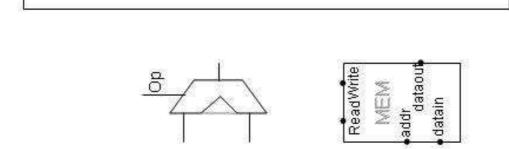

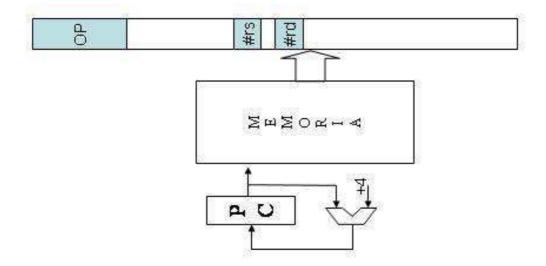

1. Si vuole implementare un processore mediante una pipeline <u>a 4 stadi (F, D, E, W)</u>, in grado di eseguire le seguenti istruzioni, il cui significato è riportato a commento (per semplicità, si faccia riferimento solo alle seguenti istruzioni trascurando ad esempio le varie tipologie di salti):

add rd, rs // rd

$$\leftarrow$$

rd+rs

lw rd, (rs) // rd  $\leftarrow$  M[rs]

sw rd, (rs) // M[rs]  $\leftarrow$  rd

Nella pagina seguente è riportato uno schema incompleto di datapath.

Si chiede di:

- 1) completare i collegamenti tra unità funzionali e registri interstadio negli stadi D, E, W inserendo eventualmente opportuni multiplexer e indicando i segnali di controllo necessari;

- 2) disegnare nel datapath l'unità di controllo (che può essere schematizzata con un ovale) e i relativi collegamenti;

- 3) disegnare accuratamente nel datapath i collegamenti dei segnali di controllo negli stadi D, E, W;

- 4) fornire per mezzo di una tabella la specifica dell'unità di controllo (i codici operativi delle istruzioni possono essere specificati in forma simbolica). [8]

## 2. Si consideri il seguente frammento di codice MIPS:

add \$t0, \$s1, \$s1

lw \$s1, 40(\$t0)

add \$t0, \$s1, \$s1

sw \$s1, 20(\$t0)

add \$t0, \$s1, \$s1

Si consideri l'implementazione con pipeline a 5 stadi (F: Fetch, D: Decode, E: Execute, M: Mem, W: Write-Back). Si chiede di:

- a) individuare in modo preciso tutte le dipendenze tra i dati

- b) tracciare il diagramma temporale delle istruzioni (indicando esplicitamente le eventuali propagazioni e, per ognuna di esse, quale dato è propagato) in ognuna delle seguenti ipotesi:

- non è disponibile alcuna unità di propagazione

- è disponibile un'unità di propagazione verso lo stadio E

- è disponibile un'unità di propagazione verso lo stadio E ed una verso lo stadio M.

Nei diagrammi, si chiede di indicare il numero di cicli di penalità.

[6]

- 3. Si consideri un processore MIPS, implementato tramite pipeline a 5 stadi, che disponga di una cache primaria e di una cache secondaria (distinte per i dati e le istruzioni). La cache primaria presenta le seguenti caratteristiche:

- numero di cicli di clock richiesti in caso di successo (hit): 1

- percentuale di successo (hit rate): 90% per le istruzioni, 70% per i dati

- penalità di fallimento: 8 cicli di clock

Per la cache secondaria valgono invece le seguenti condizioni:

- percentuale di successo (hit rate): 90% per le istruzioni, 80% per i dati

- cicli di clock per trasferire un blocco dalla cache secondaria alla cache primaria: 3

Si assuma un carico di lavoro che prevede la seguente distribuzione delle istruzioni MIPS:

lw: 20 % sw: 20 % Tipo-R: 30 % beq: 20 % j: 10 %

Si supponga inoltre che:

- il 40% delle istruzioni Tipo-R siano seguite da istruzioni che ne utilizzano il risultato:

- il 30% delle istruzioni lw siano seguite da istruzioni Tipo-R che ne utilizzano il risultato;

- il 10% delle istruzioni lw siano seguite da istruzioni sw che ne utilizzano il risultato per il calcolo dell'indirizzo;

- il 20 % delle istruzioni lw siano seguite da istruzioni sw che ne utilizzano il risultato per immagazzinarlo in memoria.

[NB: per semplicità, si trascuri il caso in cui una sw utilizza il risultato della lw sia per il calcolo dell'indirizzo sia per immagazzinarlo in memoria]

Tenendo conto dei miss di cache e delle criticità sui dati, si calcoli il CPI (numero medio di cicli di clock per istruzione) ottenuto nei due casi seguenti:

- si dispone di un'unità di propagazione solo verso lo stadio E

- si dispone di un'unità di propagazione verso lo stadio E ed una verso lo stadio M. [4]

- 4. Si consideri l'implementazione del processore con pipeline a 5 stadi (F: Fetch, D: Decode, E: Execute, M: Mem, W: Write-Back) che utilizza la predizione dinamica sui salti mediante BTB (Branch Target Buffer). Si ricorda che il BTB contiene, oltre alla statistica utilizzata per la predizione dei salti condizionati, anche l'indirizzo di destinazione predetto. Per i salti condizionati, si ipotizzi in particolare che:

- il calcolo dell'indirizzo di destinazione effettivo sia effettuato nello stadio D

- la condizione di salto sia valutata nello stadio E

Si consideri il seguente frammento di codice MIPS:

beq \$s0, \$s1, Dest

add \$t0, \$s0, \$s1

. . .

Dest: add \$t0, \$t0, \$t1

sub \$t3, \$t0, \$t0

Si chiede di tracciare il diagramma temporale delle istruzioni nell'ipotesi in cui il BTB preveda per l'istruzione beq che il salto venga effettuato ma la predizione sia errata (ovvero il salto in realtà non venga effettuato) e di indicare il numero di cicli di penalità. NB: si faccia un'ipotesi ragionevole sull'indirizzo di destinazione predetto dal BTB.

5. Nell'ambito delle tecniche di controllo con pipeline, si illustri brevemente (max 5-6 righe) la differenza tra tecniche di predizione statica e dinamica dei salti. Si consideri una tecnica di previsione dinamica realizzata mediante un automa a due stati: si discuta la gestione dei cicli mediante questa soluzione precisando (riferendosi ad un ciclo ripetuto n volte) i miglioramenti che si possono ottenere con l'adozione di un automa a quattro stati.

- 6. Si consideri un calcolatore in cui la cache della memoria centrale utilizza la tecnica di write back (è presente un dirty bit per ciascun blocco). Per ciascuno dei seguenti due casi, si dica se e quali interventi devono essere effettuati nella cache per assicurare la coerenza dei dati:

a seguito di un page fault, una pagina fisica in memoria centrale viene rimpiazzata da una nuova pagina fisica caricata dal disco;

- il processo corrente esaurisce il suo tempo di utilizzo del processore e viene sostituito da un nuovo processo. [3]

| 7. | Illustrare dettagliatamente (eventualmente aiutandosi con uno schema) la tecnica carbitraggio dei bus mediante daisy chain, spiegando inoltre da che cosa dipende la priorit tra i dispositivi. | à |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |

|    |                                                                                                                                                                                                 |   |